Home Search Collections Journals About Contact us My IOPscience

$\label{large-scale} \mbox{Large-scale SiO}_2 \mbox{ photonic crystal for high efficiency GaN LEDs by nanospherical-lens} \\ \mbox{lithography}$

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2014 Chinese Phys. B 23 028504

(http://iopscience.iop.org/1674-1056/23/2/028504)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 159.226.231.70

This content was downloaded on 12/05/2014 at 02:04

Please note that terms and conditions apply.

# Large-scale SiO<sub>2</sub> photonic crystal for high efficiency GaN LEDs by nanospherical-lens lithography\*

Wu Kui(吴 奎)<sup>a)b)</sup>, Wei Tong-Bo(魏同波)<sup>a)†</sup>, Lan Ding(蓝 鼎)<sup>c)</sup>, Zheng Hai-Yang(郑海洋)<sup>a)</sup>, Wang Jun-Xi(王军喜)<sup>a)</sup>, Luo Yi(罗 毅)<sup>b)</sup>, and Li Jin-Min(李晋闽)<sup>a)</sup>

(Received 29 August 2013; revised manuscript received 22 September 2013; published online 20 December 2013)

Wafer-scale SiO<sub>2</sub> photonic crystal (PhC) patterns (SiO<sub>2</sub> air-hole PhC, SiO<sub>2</sub>-pillar PhC) on indium tin oxide (ITO) layer of GaN-based light-emitting diode (LED) are fabricated via novel nanospherical-lens lithography. Nanoscale polystyrene spheres are self-assembled into a hexagonal closed-packed monolayer array acting as convex lens for exposure using conventional lithography instrument. The light output power is enhanced by as great as 40.5% and 61% over those of as-grown LEDs, for SiO<sub>2</sub>-hole PhC and SiO<sub>2</sub>-pillar PhC LEDs, respectively. No degradation to LED electrical properties is found due to the fact that SiO<sub>2</sub> PhC structures are fabricated on ITO current spreading electrode. For SiO<sub>2</sub>-pillar PhC LEDs, which have the largest light output power in all LEDs, no dry etching, which would introduce etching damage, was involved. Our method is demonstrated to be a simple, low cost, and high-yield technique for fabricating the PhC LEDs. Furthermore, the finite difference time domain simulation is also performed to further reveal the emission characteristics of LEDs with PhC structures.

Keywords: InGaN light-emitting diodes (LEDs), photonic crystal, nanosphere lithography, FDTD simulation

PACS: 85.60.Jb, 42.70.Qs, 81.16.Nd, 83.10.Rs DOI: 10.1088/1674-1056/23/2/028504

#### 1. Introduction

GaN-based light-emitting diodes (LEDs) have been used for general illumination/decoration, traffic lights, and LCD backlight units.<sup>[1–4]</sup> Future demands for more extensive applications require higher brightness and lower power consumption. The LED quantum efficiency is determined by both internal quantum efficiency (IQE) and light extraction efficiency (LEE). Owing to great progress in crystal quality and structure design of active layers, the IQE for blue LED has reached as high as 70%. [5] However, the EQE of LED is still limited by the total internal reflection (TIR) between LED die and external medium. Various techniques, including surfaceroughening<sup>[6]</sup> and patterned sapphire substrates,<sup>[7]</sup> have been adopted to improve the light extraction from LED device, which relies on the formation of non-parallel surface to minimize reflection. Specifically, the use of photonic crystal (PhC) structure in LED has drawn much attention, since it provides a novel method of controlling optical modes to improve the light extraction by efficiently coupling guided modes out of light-emitting diodes.<sup>[5]</sup> Generally, PhC structures have been fabricated directly in the p-GaN layer or ITO layer. [8-11] The plasma dry etching process has been reported to produce various defects, such as vacancies, impurities, and residuals, resulting in the degradation of LED electrical properties. To alleviate this degradation, an additional passivation process will be needed to polish the etching damages. On the other hand, it is worthy to note that applying PhC structure in p-GaN or ITO layer needs thick p-GaN or ITO to bear the plasma etching. Otherwise, leakage current will take place, accelerating the LED device degradation. However, a very thick p-GaN layer, with a poor crystalline quality, [12] will lead to lower optical transmission and higher working voltage, resulting in a decrease of the overall efficiency.

In addition, the height and the period of PhC structure is known to be on the order of its wavelength. [9,13] Therefore, traditional optical lithography will be inoperative to achieve this nanoscale patterning because of the optical diffraction effect. The frequently used nano-pattering methods, such as e-beam laser holography, [13] self-organized porous anodic alumina, [14] nanoimprint, [15] are used to fabricate PhC LED devices. However, the drawbacks of these three techniques include low throughput, high cost, and hardly patterning at full wafer level. As for nanoimprint, it is required to make improvement, that is, producing fewer defects, minimizing patterns at low cost and full wafer level.

In this study, we introduce a nanospherical-lens photolithography (NLP) method to fabricate SiO<sub>2</sub> PhC structures in GaN-based LEDs. The nanospheres are not directly used as etching masks, in which the space ratios of the nanospheres are hardly independently controlled, and the remnants are not

a) Semiconductor Lighting Technology Research and Development Center, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China b) Tsinghua National Laboratory for Information Science and Technology/State Key Laboratory on Integrated Optoelectronics, Tsinghua University, Beijing 100084, China

c) National Microgravity Laboratory, Institute of Mechanics, Chinese Academy of Sciences, Beijing 100190, China

<sup>\*</sup>Project supported by the National Basic Research Program of China (Grant No. 2011CB301902).

<sup>†</sup>Corresponding author. E-mail: tbwei@semi.ac.cn

<sup>© 2014</sup> Chinese Physical Society and IOP Publishing Ltd

easily eliminated. The proposed method has the advantages of low cost, high throughput, and full wafer level. Moreover, hexagonal-lattice SiO<sub>2</sub> PhC structures are directly processed on the wafers, which have been fabricated after the metal electrode deposition, avoiding the degradation of the electrical performance. Moreover, the SiO<sub>2</sub> PhC arrays can also act as passivation layer for the LEDs. The optical and electrical performances of dual structure SiO<sub>2</sub> PhCs LEDs are analyzed and discussed in detail. Finally, the finite-difference time-domain (FDTD) is employed to simulate the optical field distributions of the LEDs incorporating SiO<sub>2</sub> PhC structures.

# 2. Experiment

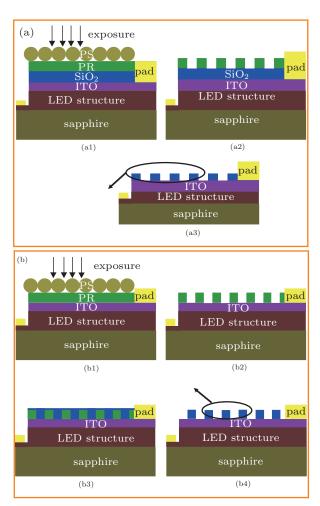

The blue InGaN/GaN LEDs with the wavelength of 445 nm were grown on c-plane sapphires by metal-organic chemical vapor deposition (MOCVD). The epitaxial LED structure is similar to that in our previous report. [16] After a 280-nm-thick ITO transparent conductive layer was deposited on the wafer, photolithography and inductively coupled plasma (ICP) etching were used to fabricate metal electrodes composed of Cr/Pt/Au (50 nm/50 nm/1500 nm) evaporated onto the ITO transparent conductive layer and the n-GaN layer by an e-beam evaporator. Figure 1 shows the schematics of the PhC LED fabrication process. For LED sample A, as shown in Fig. 1(a), the current electrode over wafer was deposited about 300-nm thick SiO<sub>2</sub> layer using plasma enhanced chemical vapor deposition (PECVD). Then, the surface was coated by 600-nm photosensitive resist (PR) AR-P 3120, followed by a hot plate bake for 15 min at 95 °C. Successively, nanospherical-lens were spin-coated on the PR, which was hexagonal close-packed monolayer of polystyrene spheres (PSs) with a diameter of 500 nm. After UV exposure about 5 s and developing about 5 s, holes each with a diameter of about 250 nm on PR were fabricated, using a conventional photolithography instrument, followed by the elimination of PS by ultrasonication in deionized water. Subsequently, the patterned PR was then baked at 110 °C for 10 min for bearing the followed ICP etching of SiO2 dielectric. The ICP etching was performed using CF4 (532 mPa) at a radio-frequency power of 40 W, for duration 110 s by STS Multiplex AOE etching. Then, the SiO<sub>2</sub> with air-hole PhC LED (SiO<sub>2</sub>-hole PhC) with 500-nm period lattice and about 250-nm air holes was successively completed. In Fig. 1(b), inverse SiO<sub>2</sub> structure PhC LEDs (sample B), were also fabricated, which consisted of SiO<sub>2</sub> nanopillars on the surfaces (called SiO<sub>2</sub>-pillar PhC). After the above NLP process of developing, 250-nm thick SiO<sub>2</sub> layer was sputtered on patterned PR using an oxford ion beam sputter at room temperature and a pressure of approximately  $1.3 \times 10^{-2}$  Pa. A lift-off process was then carried out by dissolving the PR in acetone for 30 min, retaining the arrays of SiO<sub>2</sub> nanodisk. In the lift-off process, 250-nm SiO<sub>2</sub> on the photoresist can be well lifted off, remaining the arrays of  $SiO_2$  nanodisk perfectly. Afterwards, these wafers were processed into chips with a square mesa of 45 mil<sup>2</sup> (1 mil = 0.0254 mm) in size. For comparison, an un-patterned LED with identical dimensions is also fabricated. All of the devices were fabricated from the same LED wafer, in order to eliminate the variations in the device characteristics found from wafer to wafer.

**Fig. 1.** (color online) Schematic diagrams showing the fabrication process flow chart of SiO<sub>2</sub> PhC structures in LEDs: (a) SiO<sub>2</sub> hole PhC LEDs: a(1) exposure for the current electrode over wafer with PS arrays, a(2) after developing, a(3) after dry etching; (b) SiO<sub>2</sub>-pillar PhC LEDs: b(1) exposure for the current electrode over wafer with PS array, b(2) after developing, b(3) SiO<sub>2</sub> deposition at room temperature, b(4) SiO<sub>2</sub> pillar arrays after PR lift-off in acetone.

## 3. Results and discussion

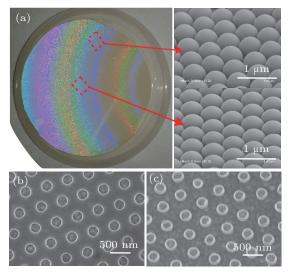

Figure 2(a) shows the optical photographs of 2-inch LED wafer (1 inch = 25.4 mm) with full spin coating PS on PR. In the close view SEM images, the hexagonally close-packed of monolayer PS arrays of 500-nm lattice can be found. The SiO<sub>2</sub> hole PhC and SiO<sub>2</sub>-pillar PhC are shown in Figs. 2(b) and 2(c), respectively, with a periodic lattice of 500 nm determined by the diameter of PS nanospheres, which is on the order of wavelength of blue LED, leading to higher LEE. [17] In experiment, we found that if the diameter of the PS is too much small (for example, 400 nm), then the NLP method cannot work because

of diffraction effect in UV-exposure process. The diameter for hole and  $SiO_2$  nanopillar trimmed with about 250 nm, are turned by the UV-exposure and developing time. So, the duty cycle was set to be a special value of 1:1, its other value will be discussed elsewhere.

**Fig. 2.** (color online) SEM images showing (a) ordered hexagonal monolayer arrays of PS on RF surface, and partial enlarged drawings of the inner and outer of the wafer; (b) the surface of SiO<sub>2</sub> hole PhC LED; (c) the surface of SiO<sub>2</sub>-pillar PhC LED.

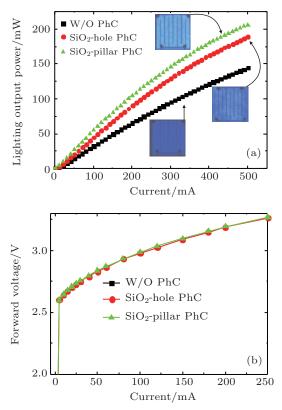

Figure 3(a) shows the light output power (LOP) of the blue LEDs with and without SiO2 PhC structures, with collecting the emitted light with a 2-inch (1 inch = 25.4 mm) integrating sphere optically coupled to a radiometrically calibrated spectrometer. The LOP of LEDs with SiO2 hole PhC, and SiO<sub>2</sub>-pillar PhC is increased by as great as 40.5% and 61%, compared with those of reference LEDs at an input current of 350 mA, respectively. The insets of Fig. 3(a) show the emission images of the corresponding LEDs operating at a low injection current of 2 mA. The SiO<sub>2</sub>-pillar PhC LED is brighter than the LEDs with SiO<sub>2</sub> hole PhC and without PhC. The improvement is attributed to the increase in LEE due to the PhC effect, which creates the cut-off frequency for the guided modes. The modes above the cut-off frequency are leaky and couple to free space. [18] The current–voltage (I-V)characteristics of the LEDs are plotted in Fig. 3(b). The forward voltages at 20-mA current are 2.70, 2.71, and 2.70 V, for SiO<sub>2</sub>-pillar PhC, SiO<sub>2</sub>-hole PhC, and without PC LED, respectively. The slopes of the *I–V* curves in the linear region, the series resistance, are also identical. This is due to the fact that SiO<sub>2</sub> PhC structures were fabricated on ITO current electrode over wafers. The LOP and I-V data have testified the fact that the fabrication process, corresponding to SiO<sub>2</sub>-pillar PhC LED, leaves the ITO intact and free of any etching damages, demonstrating a promising simple technique to improve the LEE of LEDs without any degradation of electrical properties.

**Fig. 3.** (color online) (a) Plots of light output power versus injection current and the insets show the corresponding optical microphotographs of the above LEDs operated at a low injection current of 2 mA; (b) I-V characteristics of the SiO<sub>2</sub> hole PhC LED, SiO<sub>2</sub>-pillar one, and as grown LED.

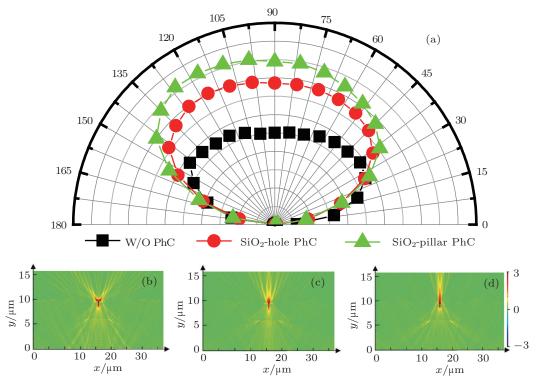

To investigate the effect of SiO<sub>2</sub> PhC on the LED angular emission profile, the chips were loaded on an aluminumbase plate and bonded with Au-wire without epoxy encapsulation. As shown in Fig. 4(a), the full-width at half-maximum (FWHM) divergence angles are 135.7°, 146.3°, and 162.2°, for the SiO<sub>2</sub>-pillar PhC LEDs, SiO<sub>2</sub>-hole PhC LEDs, and without PhC LEDs, respectively. The light from SiO<sub>2</sub>-pillar PhC LEDs exhibits more converging effect over the others and a divergence angle reduction of 26.5° compared with the light from the conventional LEDs. The divergence angle reduction is ascribed to the SiO<sub>2</sub> PhC structure to inhibit the light radiating from lateral direction, which leads to a molded flow of light rather than randomly scattered one.

Because of the symmetrical characteristic of SiO<sub>2</sub> PhC structure, a two-dimensional (2D) FDTD simulation was conducted to show the light field distribution of PhC LEDs. The model used in simulation was simplified into the one that consisted of a 150-μm sapphire substrate, a 4-μm GaN layer, a 280-nm ITO layer, followed by SiO<sub>2</sub> PhC structure being the top surface. The point radiant sources of 460-nm wavelength were set below the SiO<sub>2</sub> hole or SiO<sub>2</sub>-pillar at 3.06 μm away from GaN/sapphire interface right at the center of active layers. Only transverse electric (TE) polarization was taken into consideration, which is absolutely dominant in the GaN-based LEDs.<sup>[19]</sup> Figures 4(b)–4(d) show that the distributions of light electrical field intensities from the cross sections of LEDs with

SiO<sub>2</sub>-pillar PhC, SiO<sub>2</sub> hole PhC, and without PhC LEDs, respectively. It should be noted that the field intensity of SiO<sub>2</sub>-pillar PhC LED below the top surface appeared to be weaker,

and that of  $SiO_2$ -pillar PhC LED over the top surface showed more converging effect than those of  $SiO_2$  hole PhC LEDs and those without PhC.

Fig. 4. (color online) (a) Far-field emission patterns of the LEDs SiO<sub>2</sub> hole PhC LED, SiO<sub>2</sub>-pillar, and without PhC LEDs; FDTD simulation of light propagation in (b) LED without PhC, (c) with SiO<sub>2</sub> hole PhC LED, and (d) SiO<sub>2</sub>-pillar PhC LED.

## 4. Conclusions

In this paper, high-quality wafer-scale SiO<sub>2</sub> PhC structures on ITO layer of GaN-based light-emitting diodes (LEDs) are fabricated via a novel NLP process unitizing the focusing behavior of PS nanospheres. Significant improvement in the light output power is observed over as-grown LEDs. The proposed method demonstrates that it will not introduce any degradation to the electrical properties of the fabricated LEDs. The LEDs with SiO<sub>2</sub> pillar PhC structure exhibits the highest light output power and the most significant focusing effect, which are consistent with FDTD simulation result. This damage-free method, with great advantages of low cost and high-yield, enables them to be a promising technique for commercial production.

#### References

- [1] Liu N, Liu H, Zhu S and Giessen H 2009 Nat. Photon. 3 157

- [2] Lu Y, Yang Z J, Pan Y B, Xu K, Hu X D, Zhang B and Zhang G Y 2006 Chin. Phys. Lett. 23 256

- [3] Zhang J M, Zou D S, Xu C, Zhu Y X, Liang T, Da X L and Shen G D 2007 Chin. Phys. 16 1135

- [4] Yang L, Ma X H, Feng Q and Hao Y 2008 Chin. Phys. B 17 2696

- [5] Wierer J J, David A and Megens M M 2009 Nat. Photon. 3 163

- [6] Zhang Y, Zheng H, Wei T, Yang H, Li J, Yi X, Song X, Wang G and Li J 2012 Opt. Express 20 6808

- [7] Lin Y S and Yeh J A 2011 Appl. Phys. Express 4 092103

- [8] Sim J I, Lee B G, Yang W J, Yoon H D and Kim T G 2011 Jpn. J. Appl. Phys. 50 2101

- [9] Li K and Choi H 2011 J. Appl. Phys. 110 053104

- [10] Ng W, Leung C, Lai P and Choi H 2008 Nanotechnology 19 255302

- [11] Kwon M K, Kim J Y, Kim K S, Jung G Y, Lim W, Kim S T and Park S J 2013 ECS J. Solid State Sci. Technol. 2 P13

- [12] Oh M S, Kwon M K, Park I K, Baek S H, Park S J, Lee S and Jung J 2006 J. Cryst. Growth 289 107

- [13] Kim D H, Cho C O, Roh Y G, Jeon H, Park Y S, Cho J, Im J S, Sone C, Park Y and Choi W J 2005 Appl. Phys. Lett. 87 203508

- [14] Wildeson I H, Colby R, Ewoldt D A, Liang Z, Zakharov D N, Zaluzec N J, García E A, Stach R E and Sands T D 2010 J. Appl. Phys. 108 044303

- [15] Cho H K, Jang J, Choi J H, Choi J, Kim J, Lee J S, Lee B, Choe Y H, Lee K D and Kim S H 2006 Opt. Express 14 8654

- [16] Wei T, Wu K, Lan D, Yan Q, Chen Y, Du C, Wang J, Zeng Y and Li J 2012 Appl. Phys. Lett. 101 211111

- [17] Oder T, Kim K, Lin J and Jiang H 2004 Appl. Phys. Lett. 84 466

- [18] Lee Y J, Kim S H, Huh J, Kim G H, Lee Y H, Cho S H, Kim Y C and Do Y R 2003 Appl. Phys. Lett. 82 3779

- [19] Fan S, Villeneuve P R, Joannopoulos J and Schubert E 1997 Phys. Rev. Lett. 78 3294