Composite Structures Vol. 38, No. 1–4, pp. 525–530, 1997 © 1997 Elsevier Science Ltd. All rights reserved Printed in Great Britain 0263-8223/97/\$17.00 + 0.00

P11:S0263-8223(97)00088-3

# Effect of cracks on thermal stress and strain of a tape automated bonded package

C. M. L. Wu, J. K. L. Lai

Department of Physics and Materials Science, City University of Hong Kong, 83 Tat Chee Avenue, Hong Kong

# &

# Yongli Wu

Institute of Mechanics, Chinese Academy of Science, Beijing 100080, People's Republic of China

A tape automated bonded (TAB) package is basically a composite structure. A three-dimensional finite element fracture analysis was performed to evaluate the effects of cracks in a TAB package under thermal cycling conditions. The lead-tin solder in the outer lead bond as well as the copper beam lead were taken as elasto-plastic materials. Interface cracks between the copper beam lead and the solder were included in the analysis. It was found that the prescribed cracks created new sources of stress concentrations, which are fairly mild. This result showed that the configuration of the outer lead bonds in TAB packages is generally resilient to thermal cycling, even with the presence of defects such as cracks. © 1997 Elsevier Science Ltd.

# **INTRODUCTION**

Modern electronic assemblies consist of a few materials. For example, printed circuit boards (PCB) are usually constructed using FR-4 woven glass fibre reinforced composite plates. Because of the nature of their construction, it is appropriate to analyse these assemblies as composite structures. For example, finite element analyses have been found useful in predicting thermal and mechanical stresses in a surfacemounted component on a PCB.

Tape automated bonding (TAB) was introduced in the late 1960s, for packaging of electronic components. TAB uses a linear flex circuit beam lead pattern, in a polymer-metal cinematography format, to support, transport and perform lead interconnection to semiconductor chips. It has been considered as a viable means of reducing the cost of electronic components for the past 20 years.

The value of TAB in semiconductor fabrication has been established by its application by major international corporations. Wire-bonding assembly limits are pushed back while pad density, interconnection integrity, performance, test, and reliability are enhanced, leading to lower overall costs and a better product. TAB has been applied to the even more demanding field of very large scale integration packaging for a variety of consumer, medical, security, computer, peripheral, telecommunication, automotive and aerospace products. A comprehensive overview of TAB technology is available in ref. [1].

A TAB package is typically composed of components made up from various materials with different thermal expansion characteristics. This produces thermal stresses in the package, even under normal power cycling of the electronic equipment. On top of the thermal effects, the package is subjected to mounting constraints, resulting in externally applied stresses to the package. Repeated duty cycling can cause fatigue at joints, at interfaces between different materials, at interconnection locations or cause delimitation of the FR-4 material.

The outer leads in a TAB package are sometimes connected to PCBs or directly to liquid crystal display glass panels. The joints at the outer leads not only function as electric conduction paths, but also act as important structural members of the whole package. Prediction of thermally induced stresses towards failure of these joints is therefore critical in assessing the reliability of the TAB package. Thermal stress analysis of multi-chip packages with a flip-chip configuration and a conduction cooling module has been carried out by Darveraux et al. [2]. The authors pointed out that even if a package design is optimized to be thermal-expansion matched under operating conditions, significant thermal stresses may develop during a transient. Lau et al. [3]. have performed a stress analysis for a TAB package with a 48-lead chip. Thermally induced stresses have been calculated and critical components more prone to fatigue failure have been identified in this paper. Jog et al. [4] have performed a three-dimensional (3-D) thermal stress and strain analysis of a TAB package subjected to accelerated thermal cycling. Transient temperature, stress and strain distributions have been obtained in the package see also ref [5].

It is well known that undetectable defects such as voids may exist in all electronic connections. This is no exception to TAB joints. It is therefore important to analyse the problem of TAB with built-in defects.

In this paper, a 3-D stress and strain analysis was been carried out by including an interface crack between the outer lead and solder in the TAB package. Thermal stresses and strains have been obtained.

# FORMULATION

Generally the theory of uncoupled thermomechanics is used to analyse the temperature and thermal stresses in the TAB package. It means that the interaction between strain and temperature is ignored and the effects of change in dimension of the package on temperature distribution are negligible. The transient energy conservation equation governing the 3-D temperature distribution in a TAB assembly is

$$\rho C \, \frac{\partial T}{\partial t} = \nabla(\kappa \nabla T) + W \tag{1}$$

where  $\rho$  is the density, C is the specific heat,  $\kappa$  is the thermal conductivity of the material, T is

the temperature and W is the heat-generation rate.

The resulting temperature distribution is employed in the following simultaneous governing equations to get the stress and the strain fields in the TAB package. The stress equilibrium is given by

$$\sigma_{ii,i} = 0 \tag{2}$$

The constitutive equation for an isotropic linear elastic solid and plastic solid including thermal strain may be written as

$$\{\sigma\} = [C_e]\{\varepsilon\} - [C_e]\{\alpha\}(T - T_0)$$

(3)

$$\{d\sigma\} = [C_{ep}]\{d\varepsilon\} - [C_{ep}]\{\alpha\}dT \tag{4}$$

The strain-displacement relations are

$$\varepsilon_{ij} = \frac{1}{2} \left( u_{i,j} + u_{j,i} \right) \tag{5}$$

where  $T_0$  is the reference temperature,  $\sigma_{ij}$  is the components of the stress tensor,  $\varepsilon_{ij}$  is the component of the strain tensor,  $\alpha$  is the coefficient of thermal expansion,  $u_i$  is the components of the displacement vector,  $[C_e]$  is the elastic matrix and  $[C_{en}]$  is the plastic matrix.

Details on the theory of uncoupled thermomechanics can be found in refs [6] and [7].

The temperature distribution in the electronics package is calculated by solving the heat conduction equation (1) with the prescribed initial and boundary conditions. Displacements, strains and stresses everywhere inside the package are then determined by solving eqns (2)-(5)with the prescribed stress-displacement boundary conditions and with the calculated temperature distribution.

The determination of temperature distribution and stresses in TAB packaging is not an easy task. The finite element method [6,7] is one of the best candidates for obtaining numerical results for the temperature distribution and the thermal stresses in TAB package. We use a finite element code, ABAQUS [8], to calculate the temperature and stresses in the TAB package.

### **DESCRIPTION OF THE PROBLEM**

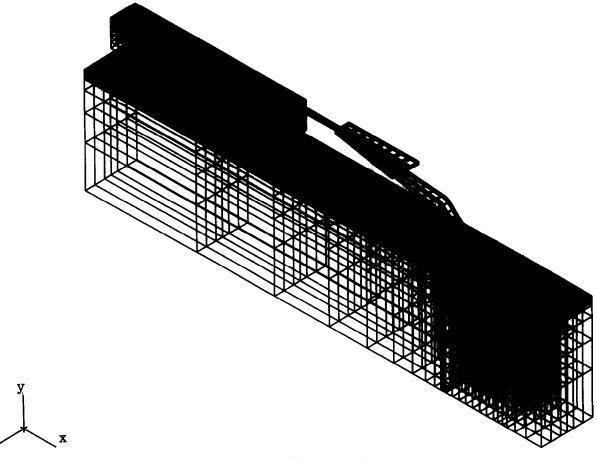

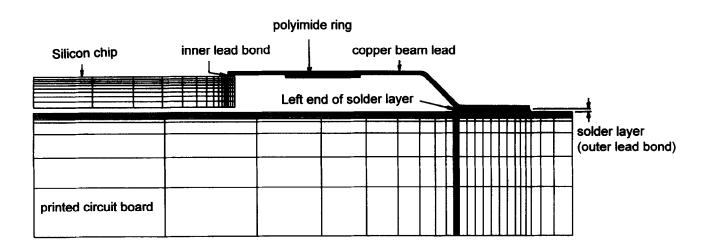

A thin slice of a TAB package was analysed in ref. [3]. In the present investigation, a similar model as that given in ref. [3] has been made and is shown in Fig. 1. Figure 2 shows the pack-

age in the x-y plane. It can be seen from this figure that the TAB package consists of six major parts: the silicon chip, the gold bump, the

polyimide ring, the copper beam lead, the leadtin solder layer, and the FR-4 PCB. The dimensions of the various components have

Fig. 1. A section of a TAB package.

Fig. 2. The TAB package in the x-y plane.

528

| Material     | $(10^{-3} \frac{\rho}{\text{g/mm}^3})$ | С<br>(J/g K) | к<br>(W/mm K) | $(10^{-6}/\mathrm{K})$ | E<br>(MPa) | v    |

|--------------|----------------------------------------|--------------|---------------|------------------------|------------|------|

| Pb-Sn solder | 8.41                                   | 0.1498       | 0.04979       | 21.0                   | 10,340     | 0.40 |

| Copper       | 8.94                                   | 0.3815       | 0.3978        | 17.0                   | 121,000    | 0.35 |

| Polyimide    | 1.53                                   | 1.09         | 0.00012       | 20.0                   | 4140       | 0.30 |

| Goĺd         | 19.3                                   | 0.1292       | 0.3151        | 15.0                   | 78,000     | 0.30 |

| Silicon      | 2.33                                   | 0.7071       | 0.1481        | 2.9                    | 131.600    | 0.30 |

| FR-4         | 3.0                                    | 0.1          | 0.000262      | 15.0                   | 11,000     | 0.28 |

Table 1. Material properties of the TAB package

been given in ref. [3]. The physical and mechanical properties for various materials in the TAB package are given in Table 1 [9].

For the present analysis, the silicon, the gold, polyimide and FR-4 are assumed to be linearelastic. The copper and solder are assumed to be isotropic and under isotropic and elasto-plastic strain-hardening rule. The strain-hardening equation used to describe the elasto-plastic stress-strain behaviour is

$$\varepsilon = \frac{\sigma}{E} + \frac{\sigma - \sigma_{y}}{\beta E} \tag{6}$$

where  $\sigma_y$  is the material yield stress and  $\beta$  is the strain-hardening parameter. For copper,  $\sigma_y = 62$  MPa,  $\beta = 0.0075$ . For lead-tin solder,  $\sigma_y = 8.27$  MPa and  $\beta = 0.1$ .

To simulate the effects due to temperature cycling, it is assumed that the TAB package is subjected to temperature variation from -55 to  $125^{\circ}$ C. Residual stresses due to soldering and other manufacturing processes are not considered. That is, the package is assumed to be stress-free at the starting temperature. Defects in the OLB solder joint are included in the form of interface edge and inner cracks. The finite element model contained 2796 3-D isoparametric elements. Each element has 20 nodal points. A total of 14,641 nodes were used in the model.

#### **RESULTS AND DISCUSSION**

Three cases were analysed in this paper. In order to compare the results of the present analysis with those of previous investigators, the configuration of the present TAB package is taken as that in ref. [3]. In case 1 of the analysis, there is no interface crack in the TAB package. The finite element mesh for this case is shown in Fig. 1. It can be seen in this figure that a thin slice of the whole TAB package is modelled. In case 2, an interface edge crack between the solder and the beam lead at the OLB is included. This crack starts at the lefthand end of the solder layer shown in Fig. 2. The length of this crack is 0.031 mm. In case 3, a different interface crack between the solder and the beam lead at the OLB is included. This crack starts at a position 0.046 mm from the left-hand end of the solder layer, and has a crack length of 0.146 mm. Apart from the temperature variation from -55 to  $125^{\circ}$ C, no external forces are imposed on the package.

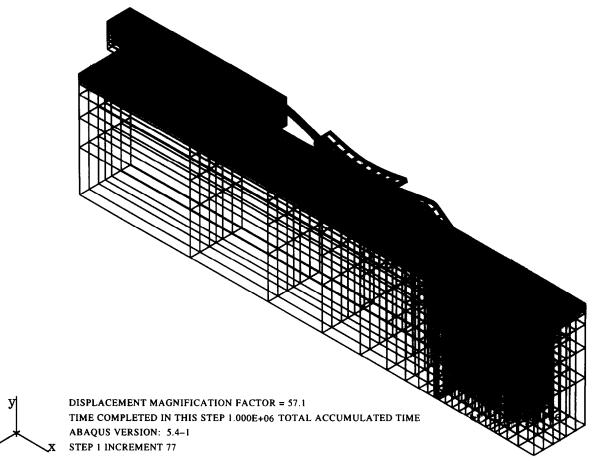

Figure 3 shows the 3-D deformation pattern of the package in case 1. By inspecting the deformation in close detail it was found that the chip was displaced further upwards away from the PCB, and that the beam lead together with the polyimide ring sagged down in the middle position. The deformation patterns in cases 2 and 3 were very similar to that in case 1 so they are not shown. However, by inspecting the deformation pattern at and near the crack, it was found that, as a result of thermal cycling, the cracks in both cases of crack inclusion in the model had been opened. This phenomenon is shown in Fig. 4, where the vertical displacements along the length of the OLB solder joint around the crack positions are given for all three cases. In general, the vertical displacement starts from a high value, gradually decreases along the solder length to a certain minimum value, and gradually increases again further along the solder length. In particular, the magnitude of vertical displacement is highest for case 2, followed by that in case 1, and lowest for that in case 3. The largest crack opening displacement occurred at the left-hand end of the solder layer for case 2, and has a value of 0.055  $\mu$ m. For case 3, the largest crack opening displacement is 0.025  $\mu$ m and occurred about half way along the crack length.

Fig. 3. Deformation of the TAB package.

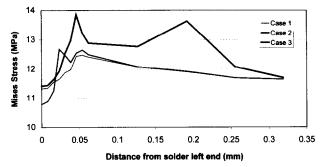

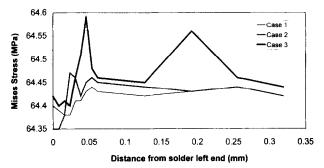

Von Mises stresses in the TAB package were obtained for all cases. The stress distribution obtained in the package for case 1 is generally comparable to that in ref. [3]. It is clear that the main concern of the present investigation is at the OLB connection. Therefore von Mises stresses are only presented in this area. In particular, von Mises stress distributions are presented at the beam lead-solder interface for the beam lead and the solder. Figure 5 shows the variation of the von Mises stress for the solder at the beam lead-solder interface along the solder length. It can be seen in case 1 of the

6 Vertical displacement (µm) 5.98 5.96 5.94 5.92 5.9 5.88 Case 3 5.86 0.05 0.15 0.25 0.3 0.35 0 0.1 0.2 Distance from solder left end (mm)

Fig. 4. Vertical displacement at the beam lead-solder interface.

analysis, i.e. without any inclusion of cracks, the magnitude of the von Mises stress is about 11.5 MPa in the main part of the solder. Again, this is comparable to the stresses obtained in ref. [3]. There exists a small stress peak near the left-hand end of the solder. This general stress distribution pattern is altered by the inclusion of cracks. As shown in the stress distribution for case 2 in Fig. 5, the stress peak now occurs very close to the prescribed crack tip. Stress increase at both crack tips was found in case 3. Since the position of peak stress where no crack was

Fig. 5. Von Mises stress distribution in the solder at the beam lead-solder interface.

Fig. 6. Von Mises stress distribution in the beam lead at the beam lead-solder interface.

present, the amount of stress increase in case 3 is fairly high.

The von Mises stress distribution for the beam lead at the beam lead-solder interface along the solder length is presented in Fig. 6. The stress level is about 64 MPa for all cases and is about the same as that in ref. [3]. The variation in stress along the solder length can be observed to be very similar to that in Fig. 5.

The present analysis has demonstrated that the inclusion of cracks at the beam lead-solder interface has created sources of stress concentrations. However, when comparing the present magnitude of stress concentrations with that created in similar studies with crack inclusions for surface mount assemblies, the present magnitude is not high, and should not be a concern. It should be noted though, that the inclusion of cracks at the solder-PCB interface is expected to produce slightly higher stress concentrations than those in the present investigation.

#### CONCLUSIONS

The effects of cracks in a TAB package under thermal cycling condition were evaluated by a 3-D finite element fracture analysis. The leadtin solder in the OLB as well as the copper beam lead were taken as elasto-plastic materials. Interface cracks between the copper beam lead and the solder were included in the analysis. The uncoupled thermomechanics formulation was used. The temperature distribution in the package was obtained, followed by the solution of stress and strain fields using the temperature distribution. It was found that the existence of cracks created additional, but mild, stress concentrations. This showed that the configuration of the OLB in TAB packages is generally resilient to thermal cycling conditions, even with the presence of defects such as cracks.

#### ACKNOWLEDGEMENTS

This work was supported by the Competitive Earmarked Research Grant of the University Grants Committee of Hong Kong Strategic through grant number 9040161.

#### REFERENCES

- 1. Lau, J. H., Erasmus, S. J. and Rice, D. W., Overview of TAB technology. In *Electronics Materials Handbook*, Vol. 1, Packaging, ASM International, 1989, pp. 274–296.

- Darveraux, R., Turlik, I., Hwang, L.T. and Reisman, A., Thermal stress analysis of a multichip package design. *IEEE Trans Components, Hybrids, Manuf. Tech*nol., 1989, CHMT-12, (4), 663-672.

- 3. Lau, J.H., Rice, D.W. and Harkings, C.G., Thermal stress analysis of TAB packages and interconnections. *IEEE Trans Components, Hybrids, Manuf. Technol.*, 1990, CHMT-13, (1), 182–187.

- 4. Jog, M.A., Cohen, I.M. and Ayyaswamy, P.S., Analysis and simulation of thermal transients and resultant stresses and strains in TAB packaging. *Trans ASME, J. Electronic Packaging*, 1993, **115**, 34–38.

- Lau, J.H. and Harkins, C.G., Thermal-stress analysis of SOIC packages and interconnections. *IEEE Trans. Components, Hybrids, Manuf. Technol.*, 1988, CHMT-11 (4), 380-389.

- 6. Lau, J. H., Thermal Stress and Strain in Microelectronics Packaging. Van Norstrand Reinhold, 1993.

- 7. Hsu, T. R., The Finite Element Method in Thermomechanics. Allen & Unwin, 1986.

- 8. ABAQUS User's Manual, Hibbitt, Karlsson & Sorensen Inc., Providence, RI, 1993.

- 9. King, J. A., Material Handbook for Hybrid Microelectronics. Artech House, Boston, 1988.